摘要

半导体技术的进步使得功率器件面临更高的电压、功率密度和结温,这对功率器件的封装的可靠性提出了更高的要求. 如何提高和检测功率器件的可靠性已经成为功率器件发展的重要任务. 提升器件封装可靠性主要围绕优化封装结构、改进芯片贴装技术和引线键合技术 3 个方向研究. 功率循环作为最贴近功率器件实际工况的可靠性测试方法,其测试技术、参数监测方法和失效机理得到广泛的研究. 对功率器件封装结构、封装技术以及功率循环机理的相关研究进行了综述,总结了近年国内外的提升封装可靠性的方法,并介绍功率循环测试的原理和钎料层、键合线的失效机理,最后对于功率器件封装的未来发展趋势进行了展望.

创新点:

(1) 从封装结构、芯片贴装和引线键合 3 方面讨论了提升功率器件封装可靠性.

(2) 总结了功率循环的控制参数、策略、检测参数和失效判据方面的研究.

0 序言

功率器件作为电力电子系统中的核心部分,起到功率转换、功率放大、功率开关、线路保护和整流等作用,被广泛应用于电力输送、高铁、电动汽车、工业控制等领域,对功率器件的性能提出更高的要求. 以 SiC 为代表的第三代半导体材料由于具有较宽的禁带宽度 (大于 2.3 eV)、更低的本征载流子浓度 (10 ~ 35 个 数 量 级 )、 更 高 的 电 击 穿 场 (4 ~20 倍)、更高的热导率 (3 ~ 13 倍) 和更大的饱和电子漂移速度等诸多优越性,成为了支撑高性能功率器件相关产业自主创新发展和转型升级的核心材料和竞争焦点.

与普通电子器件相比,高性能功率器件除了要面临更恶劣的外部环境外,还需要承受更高的电压、电流变化率和功率密度,电路中存在的寄生电感在快速变化的电流中极易产生电压过冲和振荡现象,造成电压应力、电磁干扰和损耗的增加,且更高的功率密度也意味着器件将承受更高的结温.因此,器件的封装可靠性已经成为了限制器件性能的重要制约因素.

在实际工况下,功率器件的寿命有时可达数十年,对于功率器件的可靠性测试需要通过加速老化试验来实现. 其中功率循环试验 (power cycling test) 作为考核功率器件可靠性最重要的试验,通过外部电流的导通和断开模拟器件在实际工况的开关过程,以器件中的芯片为热源,在不改变失效机理的基础上加速老化. 功率循环试验中器件在循环的外部负载电流下,结温发生周期性波动,由于各层材料间存在热膨胀系数不匹配引发器件的失效.

近些年,随着第三代半导体在新能源汽车、移动通信及轨道交通等领域日益广泛的应用,依托功率循环测试技术的功率器件可靠性分析与失效行为等方面的研究得到了大量学者的广泛关注,相关测试技术与研究也取得了新的进展.文中从功率器件的封装结构入手,介绍了器件的结构和对可靠性至关重要的芯片贴装技术和引线键合技术,同时围绕功率循环的原理、参数监测和失效机理进行分析,最后对提高功率器件可靠性及功率循环检测准确性的潜在研究方向进行了展望.

1 功率模块封装

1.1 功率模块封装结构

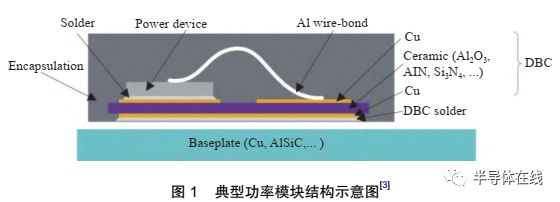

典型的功率模块结构如图 1 所示,底部通常使用钎料连接散热底板和表面覆金属的陶瓷基板,一般是覆铜陶瓷基板 (direct-bonded copper,DBC).DBC 板为芯片提供电气绝缘、耐蚀保护、机械支撑、散热通道等,其中以 Al2O3,AlN 和 Si3N4 陶瓷基板应用最为广泛. DBC 上侧通过钎料和功率芯片连接,芯片与外部端子之间由引线键合连接,整个模块用环氧树脂塑封料进行塑封. 底板通常采用 Cu 或 AlSiC 作为底座,并通过热扩散使整个模块温度分布均匀.功率模块外部通过塑封将芯片与外界环境污染和湿气隔绝,常用的塑封剂主要成分是二氧化硅和环氧树脂. 目前,欧洲制造商生产的功率模块中 70% ~ 80% 均属于该结构,在亚洲制造的模块中应用也很普遍.

随着对高功率密度和电压等级需求的增加,传统功率器件的封装结构已经不能满足要求. 传统的硅芯片器件最高结温不超过 175 ℃,而第三代半导体器件中如 SiC 功率器件理论上已经可以适应300 ℃ 的工作结温,还具有更高的开关速率和更高的封装密度,这些特点对器件的寄生电感、散热能力和热机械可靠性等方面提出了更高的要求. 目前围绕功率器件的封装需求,研究人员在传统封装结构的基础上提出了一些新的改进,进一步提升了功率器件的性能.

1.1.1 无键合线单面结构

功率模块封装大多采用引线键合结构实现模块内电流导通,然而它的缺点在于,需要在基板上增加接合区域以形成互连路径,并产生寄生电感降低器件可靠性,SiC 器件的高开关速度放大了该影响,传统键合线连接方式成为了限制负载电流能力和可靠性的瓶颈,因此无键合线的封装设计成为了改善功率模块封装结构的重要研究方向.

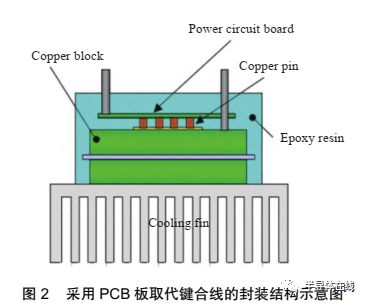

Ikeda 等人为实现高密度、高可靠性的 SiC功率器件封装,取消了键合线和底板,采用铜针和印制电路板 (printed circuit board, PCB) 代替键合线进行连接,在陶瓷表面设计了厚铜块,从而增加导热速率,通过 PCB 板和 DBC 板产生的层叠电流抵消部分电感,并采用新型环氧树脂代替传统硅胶,结构如图 2 所示. 由于铜材料的电阻更低,并且电路径更短,芯片表面上的这些铜针连接比传统的键合线结构能够承受更大的电流,而刚性的环氧树脂与软的硅胶相比可以降低每个循环中的应变幅度.

Stabach 等人采用了大面积的薄金属板代替键合线与芯片连接,其金属板刻有与芯片匹配的图案,该结构除了降低电感和体积之外,比起键合线需要逐点进行连接,金属板只需一次连接,封装效率也得到了提高. Stockmeier 等人采用 SKiN 布线技术,即采用两侧都有图案化金属层的柔性电路板代替键合线进行互连,柔性板将模块分为上下两层,其中上层为逻辑侧,主要承受辅助和感应信号,下侧为功率侧,承载负载电流,并用银颗粒烧结代替传统钎料,结构如图 3 所示,该结构的特点在于柔性电路板与芯片的接触面积远大于引线键合的点互连,热传导得到改善,因此具有更高的功率循环寿命,且柔性互连占用空间更小,使模块体积得以精简.传统键合线工艺引入较大的寄生电感,在面对高性能功率器件大的电流变化率时会引起电压过冲、振荡等问题. 取消键合线连接可降低寄生电感,还使器件上表面成为潜在的散热通道,为解决高性能器件散热问题提供了方向.

1.1.2 双面散热结构

随着器件功率密度和结温的上升,提升器件散热能力成为了提高可靠性的关键之一,传统器件由于采用引线键合技术,上表面无法作为散热通道.将上表面作为散热通道可增强器件的散热能力、降低结温进而提升可靠性,成为改善封装可靠性的途径之一.

Zhu 等人提出了一种利用压力接触取代键合线和钎料的 press-pack 封装方法,如图 4 所示, 该方法引入了被称为“Fuzz Button”的微型柔性压针,在使器件中的压力均匀分布的同时还降低了寄生电感;该结构中,SiC 芯片压接在钼基板上,“Fuzzbutton”将芯片栅极和源极与上基板连接,上下两层冷却采用液冷,经仿真得到的冷却效果优异,在总耗散功率为 60 W 时最大结温仅为 85 ℃.

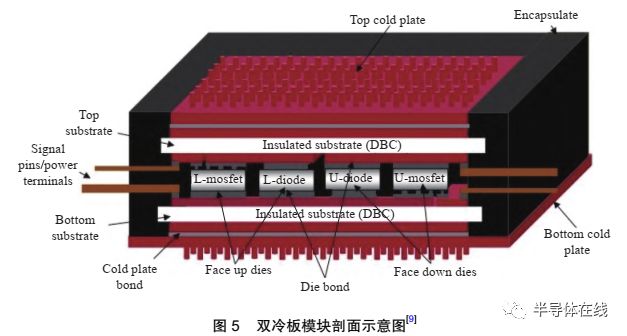

Liang 采用平面键合 (planar-bond-all,PBA)的方式取代了键合线,实现了芯片与外部的互连,并在芯片两侧均采取 DBC 连接,两 DBC 外侧均与热沉连接,以这种方式实现了双通道散热,模块结构示意如图 5 所示,经测试得到该结构热阻比传统单面散热结构降低了 38%,说明其散热能力得到提升.

除上述设计外,还有双金属基复合基板双面散热、压接封装双面散热、引线框架连接双面散热等多种实现双散热通道的封装设计. 具有更多维度散热通道的封装结构也在开发当中,如 Boteler 等人设计了可以四面散热的封装结构,这为未来通过封装结构改善器件散热性能提供了新思路.

1.1.3 多层陶瓷基板堆叠

传统封装结构在陶瓷板、陶瓷板表面金属和塑封剂三结合点处具有峰值电场. SiC 功率器件高功率密度的特点会增加电场密度,因而在峰值电场处会有击穿风险,发生局部放电,而重复的局部放电会导致绝缘失效,从而降低功率模块寿命.

Dimarino 等人采用了具有更好绝缘性能和更好的热循环能力的 DBA 板代替 DBC 板,其中陶瓷层选用 1 mm 厚 AlN,通常认为该厚度 AlN 具有足够的绝缘能力,但在面对 SiC 功率模块的峰值电场处仍有可能发生击穿,因此该研究通过将两层DBA 板以烧结银作为连接层进行连接,使得峰值电场降低了 27%,该结构另一特点是取消了底板,使 DBA 基板直接进行冷却. 基板的堆叠虽然会导致芯片散热热阻增加,但基板直接冷却和取消厚度较大的底板带来的热阻改善可以实现整体热阻的降低. 经稳态热仿真得到在单个 MOSFET 芯片功率损失 200 W,换热系数 5 000 W/(m2·K) 条件下,芯片结温与传统结构相比降幅可达 15%,表明该结构在改善了峰值电场问题的同时也具备更良好的散热能力.

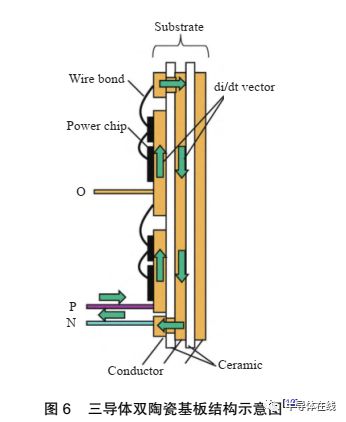

Tanimoto 等人设计了图 6 的模块结构,该结构具有 3 个金属层和两个陶瓷层,采用 Au-Sn 钎料将基板焊接到铜底板上,通过中间金属层的反平行电流,有效地降低了寄生回路电感,并且仅略微增加结温 (升高 2 ℃),对散热的影响基本可忽略;Chen 等人 则提出了一种混合封装的设计,将芯片嵌入 PCB 板,再将 PCB 板焊接在 DBC 板上,如图 7 所示,该结构为电路和结构设计提供额外的自由度,通过优化栅极连接、电流回路和驱动位置从而降低寄生电感.

1.2 芯片贴装技术

功率器件的封装材料需要面对循环的温度变化带来的热应力,传统的硅器件芯片贴装材料主要包括无铅钎料和导电胶,但它们的熔点和 SiC 芯片可承受温度相比均过低,无法满足 SiC 器件的应用需求. 目前适用于 SiC 等高性能功率器件的耐高温芯片贴装方法主要有传统钎焊连接、瞬态液相连接、纳米金属烧结.

1.2.1 传统钎焊连接

目前已被研究并得到一定应用的无铅高温钎料主要包括 Zn-Al 基和 Au 基等.

Zn-Al 合金共晶点温度为 381 ℃,具有优良的导热导电性能,且 Zn 和 Al 元素自然界储量丰富,成本低廉,是具有价格优势的一类钎料,但是该类钎料连接温度过高 (高达 400 ℃),且 Zn 元素易与氧结合,降低钎料的润湿性,目前对于该钎料通常采用添加微量元素如 In 和 Ga 等元素改善其润湿性. Yamada 等人 通过 RF 等离子体去除 Zn-Al焊 片 表 面 的 氧 化 物 , 在 真 空 条 件 下 溅 射 沉 积50 nm 厚度的铜薄膜,经过该处理的焊片得到的接头与未经处理得到的接头相比,孔隙和裂纹数目减少,说明润湿得到改善. Tanimoto 等人通过向Zn-5Al 合金加入少量 Ge 元素改善润湿性,得到了在-40 ~ 250 ℃ 下进行热循环 3 000 次后依旧具有18.5 MPa 抗剪强度的接头,但是目前较少有研究改变其较高的连接温度,该钎料进行大规模应用,仍是有待克服的难题.

金基钎料耐腐蚀性强,与铜和镍润湿性好,且高温下较为稳定,随着高性能功率器件的发展受到越来越多的关注,目前应用较多的金基钎料主要包括 Au-Si,Au-Sn 和 Au-Ge 等. Au-Si 钎料中 Si 元素质量分数为 2.85%,共晶温度 363 ℃,具有优秀的抗电迁移能力和导热导电性;Au-Sn 钎料中的Sn 元素质量分数为 20%,共晶温度 278 ℃,抗氧化性能强,在钎焊过程中无需助焊剂,因而符合部分高端电子产品无助焊剂的需求 ;Au-Ge 钎料中Ge 元素质量分数为 12%,共晶温度 361 ℃. 对于更高服役温度的钎料, Au-Ga,Au-Ag 和 Au-In 等合金体系受到研究者的关注. Liu 等人设计并制备了熔点为 450 ℃ 的 Au-30Ga 钎料,发现其具有优秀的导热导电性能,且在无助焊剂的情况下依旧保持良好的润湿性.

金基钎料存在的主要问题在于,大多数金基钎料脆性高,难以使用常规钎料的制备方法生产,且金基钎料中金含量高,使用成本高. 对于脆性较高的金基钎料,主要的制备方法包括叠层冷轧法、铸造拉拔轧制法、急冷甩带快速凝固法和电镀沉积法等,可以通过增加其它合金元素,从而降低金含量实现降低钎料成本,除 Si,Sn,Ge 和 Ga 等元素外,其它合金元素和颗粒增强相对钎料组织和性能影响的研究仍有待完善.

1.2.2 瞬态液相连接

瞬态液相 (transient liquid phase, TLP) 连接最早主要用于连接镍基、钴基等熔点较高的耐高温合金,原理是通过施加一定的压力与温度,使得低熔点钎料层熔化,溶质原子以扩散的方式与高熔点基体生成金属间化合物 (intermetallic compound,IMC),保持一段时间直至钎料层全部转化为 IMC 层,该方法得到的全 IMC 接头耐高温能力显著强于传统高温钎料,但是其缺点是扩散反应速率较慢,且连接层成分在高温下随时间也会发生变化,需要进行控制.

为解决该方法存在的问题,Li 等人结合超声波处理的方法,利用超声波带来的高温高压可使高熔点材料快速溶解至液态钎料中,造成过饱和状态,从而使冷却过程中的 IMC 生成速度大大提高.使用频率为 20 kHz,功率为 750 W 的超声波进行连接,在常温下仅用数秒就形成了全金属化合物层;Hu 等人则尝试以另一种方式改进这一缺点,制备了锡包裹铜颗粒制成的预成型片,如图 8 所示,在连接时加热至锡熔点之上,使锡熔化并与铜扩散生成金属间化合物,在 250 ℃ 下仅需保温40 min 就获得了可承受 676 ℃ 工作温度的接头,该方法在增大了反应接触面的同时还减小了扩散距离,进而缩短了连接时间.

1.2.3 纳米金属烧结

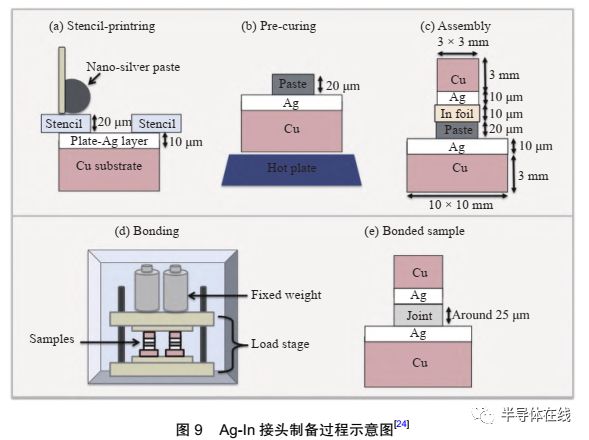

银和铜具有良好的电、热以及力学性能,但熔点较高,利用金属纳米颗粒的表面效应,可在较低温度 (200 ~ 350 ℃) 和一定压力的辅助下实现耐高温连接. 目前提高纳米焊膏的涂覆性、抗电迁移能力、降低连接压力和温度、提高连接速度以及减少成本是实际应用中遇到的主要挑战. 在烧结过程中通常采用一定的压力降低接头中的孔隙率,防止接头过早失效,但压力过大会导致芯片损坏. 为解决压力和孔隙率之间的矛盾,Yang 等人将瞬态液相键合技术与烧结纳米银浆相结合,通过将铟箔放置在两种纳米银浆之间,在保持高熔融温度的同时,在烧结接头和铜衬底之间制备出具有低孔隙率和良好润湿性的 Ag-In 接头,接头制备方法如图 9 所示;Alayli 等人将火花等离子体烧结工艺(SPS) 应用于纳米银烧结,使烧结压力从原先的 33MPa 减小至 3 MPa,并且烧结时间也由 5 min 缩短至 1 min.

纳米铜成本相比纳米银成本更低,且抗电迁移能力更强,但纳米铜颗粒在空气中极易氧化为相对稳定的 CuO/Cu2O,阻碍 Cu 原子间的扩散,且降低电导率和烧结密度,在其大规模应用之前其不耐氧化的问题仍有待解决.为提升其耐氧化能力,迟聪聪等人用油酸、柠檬酸和聚乙烯吡咯烷酮对纳米铜进行表面包覆改性,成功制备出了在空气中放置 30 d 未出现氧化现象、在室温到 243 ℃ 之内均能保持热稳定性的纳米铜颗粒;Ji 等人采用核壳结构,通过在纳米铜表面生长出抗氧化能力强的薄壳,从而提升纳米颗粒的抗氧化能力,制备了具有Cu-Ag 核壳结构的纳米颗粒,并通过超声辅助在180 ℃ 下烧结得到了具有54.27 MPa 抗剪强度的接头. 徐瑜等人通过甲酸溶液对纳米铜颗粒进行 10 min 预处理,并在 300 ℃、体积分数为 5%:95% 的氢气氩气混合保护气体下无压烧结 30 min,得到了抗剪强度为 16.18 MPa 的接头,该接头在200 ℃ 空气中经过 200 h 高温老化试验,强度仍保持在 9.38 MPa,验证了接头在高温大气条件下的强度受氧化影响较小.

1.3 引线键合技术

功率模块内部的半导体芯片表面、DBC 表面金属化层与某些功率端子之间需要互连实现电气连接,键合线互连由于工序灵活、可适应各种不同的布局,80% 以上的半导体封装均采用键合线互连.

引线键合常用的引线材料分别包括金、铝和铜等,由于金线成本偏高,较少用于功率模块之中. 铝线键合工艺成熟、成本较低,至今仍是应用最为广泛的键合方法,但铝和半导体芯片的热膨胀系数失配较大,在经长时间服役后引起热疲劳,使键合线产生裂纹甚至脱落,进而导致模块失效. 与铝相比,铜具有更高的屈服强度、更适应芯片的热膨胀系数、更高的电导率和热导率等优势,因此采用铜键合线的模块可以实现较高的功率循环寿命,但是铜线具有更高的硬度,芯片表面需制作较厚的铜层,且需要更高的键合压力和能量才能完成连接,这些都可能使较薄芯片产生裂纹. 此外,铜线难以与铝金属化的芯片表面进行连接,需要额外对芯片进行铜金属化处理,如采用物理气相沉积或化学电镀处理,增加了工艺的复杂度,制约了铜键合线的应用.镀铝铜线 (Al-Cu) 则不需要对芯片顶部采取额外的金属化工艺,结合了铜优异电学性能和铝线适于批量生产的优点,在降低了电阻率的同时增强了热导率,显著增强了其功率循环可靠性.

Ling 等人对比了铝、铜和铝-铜键合线之间的功率循环寿命和键合工艺,得到铜的寿命是铝的10 倍,铝-铜键合线是铝的 3 ~ 4 倍. 虽然铝-铜键合线寿命低于铜,但其工艺要求和成本大大降低,芯片表面的金属化难度减小. 在铜键合线的工艺更加成熟前,铝-铜键合可作为一种过渡互连方法.除键合线材料之外,键合线的形状、高度和长度对功率器件的可靠性也有显著的影响. Zhao 等人通过有限元分析,对比了弧形、梯形、抛物线形键合线的电热和热机械行为,发现不同形状键合线的温度分布没有明显差异,但应力差异很大,弧形、梯形、抛物线形键合线的最大应力分别为93.22 ,76.73 和 106.1 MPa,因此认为可以通过优化键合线形状,提升功率器件的可靠性;Celnikier 等人建立了键合线长度、温度、电流密度和键合线位移的电热力学模型,计算了 3 种长度的键合线分别在 3 种电流密度下的位移,发现最佳长度应随着功率密度的增加而减少,通过测量实际键合线的位移,发现与该模型展现出了较好的一致性.

2 功率器件功率循环

与其它可靠性测试方法 (如温度循环试验) 相比,功率循环测试以芯片为热源,更为接近实际工况,是评估器件可靠性的最主要方式. 在功率循环中,被测器件与工况类似地被安装在散热器上,通入一定占空比的电流,使结温 Tvj 在电流导通时间ton 内升温到预期最大结温 Tvjmax,同时全程以水冷或风冷的方式使得器件在电流断开时间 toff 内降温至最小结温 Tvjmin,由此带来结温的周期性变化,以提前诱发器件失效.

2.1 功率循环测试技术

2.1.1 控制参数及策略

在功率循环试验中,导致失效的直接激励源是结温变化 ΔTvj 和最大结温 Tvjmax,通常通过控制ton 和负载电流 Iload 间接控制结温变化和最大结温.欧洲 AQG 324 标准规定功率循环中电流导通时间 ton 小于 5 s 时考核的是芯片周围连接处,称为秒级循环;ton 大于 15 s 时考核的是远离芯片的连接处,称为分钟级循环;陈杰等人研究了不同 ton 对于失效模式的影响和失效机理,控制器件在相同电热环境下仅改变 ton,发现随 ton 从 1 s 变为 2 s,键合线键脚的温度波动减小,钎料层温度波动增大,首先失效位置由键合线转为钎料层,说明 ton 通过影响温度分布的方式改变失效机理.

在开始功率循环前还需要选择电流激励方法以及控制策略. 最常用的电流激励方法是 DC 功率循环电路,即在 ton 内保持导通状态,通过导通损耗加热. 而在功率器件的实际应用中,往往是以脉冲宽带调制 (pulse width modulation, PWM) 控制,在工作过程中频繁的切换状态,由开关损耗和导通损耗共同加热,如图 10 所示, 其中 DC 电路相对简单,PWM 电路复杂且结温准确测量难度较大;Tounsi 等 人 在 环 境 温 度 为 80 ℃、 结 温 波 动ΔTj 为 70 K 的条件下,测试了 PWM 电路对器件的静态参数及动态参数,发现与 DC 电路无明显差异;谢露红等人归纳总结了在两种电路下的失效方式,发现其失效机理并无太大差别,而 DC 功率循环具有电路简单,结温测量准确的优点,目前仍旧是主流的的测试方法.

功率循环的控制策略对试验结果也会产生重要影响,在不同控制策略下的模块寿命最多可相差3 倍. 分别提出了严苛性不同的控制策略,常见的4 种严苛性由高到低依次是控制 ton 不变、控制ΔTc(壳温变化量) 不变、ΔPv(功率损耗) 不变、ΔTj 不变. 其中恒定 ton 作为最苛刻的策略,同时也是欧洲 AQG 324 标准承认的唯一策略. 早期的国内标准如 GB/T 29332—2012 允许采取控制壳温恒定或随结温变化的策略,分别考核键合线和焊料层;而在 2021 年发布的 QCT 1136—2020 中则改为了与欧洲标准类似的秒级和分钟级测试,但是与其不同的是,国内标准选取的控制策略为保持 ΔTj 不变,且固定为 100 ℃,但无论 QCT 1136 —2020 还是AQG 324,均未针对 SiC 器件进行单独的测试标准说明.

除上述参数之外,结温测量的延迟时间如果设置不当也会造成重大的误差. 对于功率半导体器件,在负载电流切断后载流子需要一定时间复合,从而重建电场,如果在这时立刻测量结温则会导致测量结温偏高,而如果延迟时间过长,由于散热器作用结温会下降;Herold 等人 计算了不同结温误差导致的寿命误差,发现对于结温波动为 90 ℃、最小结温为 25 ℃ 时,5 ℃ 的误差可以导致 27% 的寿命误差;Herold 等人提出可以根据延迟时间和结温变化量的正比关系,从后续温度反推最高结温.为准确测量结温,需要设定一定的测量延迟时间.邓二平等人研究了测量延迟对于结温测量准确性的影响,并提出应从两方面解决测量延时问题,一是要解决寄生电感问题,降低测试回路对测量延时的影响,二是测试设备需具有较高的抗干扰能力和足够的采样率.

2.1.2 参数监测及失效判据

在功率循环中除了控制初始参数,与被测器件失效相关的参数的监测也十分重要. 以绝缘栅双极型晶体管 (insulated gate bipolar transistor,IGBT) 器件为例,根据欧洲 AQG 324 标准,失效的判据是:热 阻 Rth 提 升 至 初 始 值 的 120% 或 者 饱 和 压 降VCE 提升至初始值的 105% 即判定为失效,如图 11所示,其中 VCE 用来监测键合线失效,Rth 用来监测芯片到底板之间的封装完整性. 试验期间,VCE 被实时监控,可直接在电路中测得. 热阻以结到壳热阻 Rthjc 为例,定义如式 (1) 所示, 其中壳温Tc和功率 Pv 通过在线测量获得,问题在于结温Tj 需要在不破坏封装结构的基础上进行准确测量,目前存在的结温测量方法包括红外相机测量法、热电偶测量法、芯片集成温度传感器法和温敏电参数法等,其中温敏电参数法由于不需要对芯片或封装进行额外操作,因而泛用性最广,受到最多的关注. 以温敏电参数法为例,该方法本质是通过选定并测量一种受温度影响的器件参数作为温度敏感参数 (temperature sensitive electrical parameter,TSEP) 建立该参数与结温之间的关系,进而模拟结温的变化.

在功率循环试验中较为常见的温敏参数方法是小电流下饱和压降法,根据半导体的固有特性,在小电流下的饱和压降 VCE 与结温呈线性关系,因此该方法首先通过外部加热功率模块使其温度均匀,然后测定此时的饱和压降,分别在 3 ~ 5 个温度下测量即可得到反应结温和饱和压降关系的k 曲线. 在功率循环每个循环中负载电流断开时,向线路中通入小电流 Isense,得到小电流下的饱和压降 VCE,代入 k 曲线算得此时的结温 Tj.

除 了 利 用 饱 和 压 降 测 量 结 温 , 对 于 具 有MOS 结构的器件 (如 MOSFET 和 IGBT),其栅极阈值电压也是有效的温敏电参数,温度校准方法与饱和压降类似. Zeng 等人研究了两种测量方法的差异,在相同条件下分别用两种参数测量结温,发现使用栅极阈值电压始终高于饱和压降法获得的结温,如图 12 所示,可以看到随电流的增大,除了结温整体上升之外,两种方法得到的结温差也在上升,这主要是由于芯片横向的温度梯度在逐渐增大.

由于 SiC 材料自身的特性,SiC 器件的栅极存在阈值电压不稳定性,随着功率循环的进行阈值电压会发生漂移,影响相应结温测量方法的准确性.目前受到广泛认可的 SiC 功率器件结温测量方法是利用器件体二极管在小电流下的温度特性,通过在测量结温时给栅极施加足够负电压,使反向测量电流全部流经体二极管,从而避免阈值电压的偏移影响结温测量,但是该方法不能用于带有反并联二极管的 SiC 器件,因为反并联二极管会将测量电流分流,无法得到准确的测量电压,因而仍需要开发新的测量结温方法.

在实际工作和功率循环过程中,半导体芯片由于传导和开关损耗被加热,使得芯片中心温度高于边缘温度. 过去由于芯片产热相对较少,温度梯度还不明显,但随着芯片功率密度的不断上升,芯片中心和边缘温差很容易达到 40 K,这种变化可能使芯片钎料层的退化从四角转化为从中心开始,这一改变使得芯片上的温度梯度成为需要被考虑到的要素之一.

Schmidt 等人通过 MAKENET 预处理器建立了被测系统 (电源模块和散热片) 的三维模型,在利用饱和压降法获得了芯片平均结温的基础上,对于芯片的每个节点,都可以使用电气网络求解器PSpice 来计算温度,得到的模拟结果与红外测量结果较为接近.

陈杰则利用了饱和压降法和栅极阈值电压法的物理意义,即饱和压降主要反映集电极侧PN 结处的温度,栅极阈值电压主要反映的是发射极侧沟道区的温度,结合这两个信息提出了计算芯片纵向温度梯度的方法.

除 Rth 和 Vce 这两个常用失效判据外,近年来的研究中也陆续有关于其它判据的报道. 石巍选取栅极峰值电流 Igpeak 的减小作为判据,建立了关于 Igpeak 和键合线老化程度之间的定量关系,通过外加传感器测量和电阻对电流采样得到该值;孙鹏菊等人 以集电极和发射极两端直连时得到的短路电流 Isc 作为判据,构建了键合线相关寄生参数的等效电阻网络模型,并分析了键合线老化情况与电阻网络状态之间的对应关系,从而将 Isc 作为判断键合线状况的判据之一;模块跨导 gm 作为反映接合线健康状况的参数之一,也可被用来监测键合线的失效,Wang 等人推导出模块跨导的数学模型,建立了模块跨导与键合线参数之间的关系,表明模块跨导随着键合线缺陷的增加而减小,并提出了一种脉冲斜坡驱动电路提取模块跨导,进而监

控键合线的状态.

2.2 功率模块失效机理与相关研究

2.2.1 钎料层失效

钎料层的疲劳失效原因常见可分为空洞和裂纹. 空洞的产生是在连接过程中由于无铅焊点的回流效应而导致的难以避免的缺陷,且会随着循环往复的温度变化发生长大和增多;空洞会使局部温度梯度升高、应力上升并阻碍散热,显著提高结温形成热斑,甚至导致器件烧毁. 裂纹则是由热膨胀系数不匹配造成的剪切应力产生的,随着钎料层承受循环热应力,裂纹会不断生长造成分层现象. 裂纹和空洞的增加均会显著提高芯片的最大结温,产生正反馈加速钎料层疲劳和键合线的失效.

钎料层中空洞大小、数量和分布位置由于对可靠性影响较大,因而是研究者关注的重点. Li 等人 研究了在使用 SAC305 钎料焊接过程中,基板铜晶粒大小对空洞数量的影响,通过提前给铜基板进行退火改变其铜晶粒大小,然后对比在不同晶粒大小的铜基板上焊点的空洞的演化规律,得出了铜晶粒尺寸减小会产生更多空洞的结论;孙海峰等人使用 COMSOL 建立了功率模块的三维模型,并研究了空洞大小和位置对模块温度的影响,发现当空洞位于上钎料层时对温度分布影响较大,且空洞半径越大,温度升高幅度也越大.

裂纹的生长会造成钎料层热阻的增大,江南等人基于 2D 有限元分析研究了裂纹长度对热阻的影响,发现在裂纹萌生初期,热阻变化较小,但当裂纹长度比例达到钎料层边长 8% 时,芯片热阻会以指数形式增大. 关于如何确定裂纹的位置,郭秋亚提出了可以通过结构函数铜层的偏移量大小判断裂纹的大小,通过铜层的斜率判断裂纹的位置.

2.2.2 键合线失效

键合线疲劳失效通常分为键合线断裂和脱落,显微镜下的形貌如图 13 所示. 键合线产生裂纹是由于在循环热应力下,键合线的高度和长度随之发生变化,其位移可达 5 ~ 50 μm,导致根部弯曲变形进而出现裂纹,引发断裂;而键合线的脱落的原因主要是由于键合线和芯片表面热膨胀系数相差较大,产生的剪切应力作用使键合区域出现裂纹,最终导致键合线脱落.

为 探 究 电 流 频 率 对 键 合 线 失 效 的 影 响 ,Czerny 等人用激光多普勒测振仪测试了不同频率的工作电流下功率器件各部位的位移情况,结果如图 14 所示,发现随频率降低,位移增大,最大位移发生在二极管键合线上. 电流频率对可靠性的影响通常被忽略不计,但在频率较低时,二极管引线由于电流变化引发的位移已超过总位移的十分之一,应被视为影响键合线失效的因素之一.

如前文所说,通常以 VCE 作为监控键合线失效的参数,为探究在功率循环过程中键合线的老化过程与 VCE 间的关系,Dornic 等人跟踪了功率循环过程中键合线裂纹的生长,发现其增长与 VCE 的增长趋势一致,均在功率循环早期快速增长,然后以线性增长,至循环末期以指数增长至失效,据此推测 VCE 的变化与键合线裂纹直接相关,但其发生关联的机理仍不清晰.

关于键合线失效机理和失效判据,研究人员已进行了大量的工作,但是关于键合线微观组织在失效过程中的变化、失效过程中裂纹生长对器件参数的影响方面研究仍较少,有待进一步研究.

3 结束语

(1) 针对功率器件的封装和功率循环测试进行了综述,综合近年来的研究,总结出了两个可提升封装可靠性的方向,一是改进封装结构,针对功率器件散热面积有限、器件功率受限的问题采取重新设计基板、取消键合线互连以及双面散热等方法改善散热效率,降低模块热阻;二是改进封装互连材料和方法.

(2) 钎料层和键合线是器件正常工作导致的失效高发位置,在键合线方面,研究者们从键合线的材料、形状和高度等方面进行优化;在钎料层方面,连接材料成分的改进、与外加场 (如超声波处理) 结合都取得了一定的成果.

(3) 列举了功率循环试验中需要控制和监控的参数,分析了功率循环试验中最为常见的两类失效.

4 未来展望

(1) 提升功率器件的散热能力.发挥高性能功率器件的潜力,提高器件的散热能力是必然趋势. 在封装结构方面,设计无键合线的多维散热结构,降低寄生电感、增加散热路径;在材料方面,在不改变整体性能的基础上,选取导热性能更好的材料.

(2) 提高功率循环中结温测量的准确性. 高性能功率器件带来不可忽视的结温梯度,但目前功率循环试验中的常用的结温测量方式得到的都是平均结温. 为了更好的研究器件失效的过程,有必要设计一种可以在线准确获得结温梯度的方法.

(3) 研究新型封装结构的失效机理. 关于新型封装结构失效机理的研究尚不多见,对其进行相应研究有利于为新封装结构的应用和改进提供思路.

(4) 分析多方面因素综合作用下的功率器件失效过程和机理. 模块在实际的工作中不仅涉及热应力,同时还受振动、湿度等因素影响,现有研究主要集中在温度对器件可靠性的影响,较少分析多种因素共同作用下的失效机理.